# SC8F072 User Manual

Enhanced Flash 8-bit CMOS Microcontroller Rev.1.0.5

Please note the following CMS IP policy

- \*China Micro Semicon Co., Ltd. (hereinafter referred to as the Company) has applied for patents and holds absolute legal rights and interests. The patent rights associated with the Company's MCUs or other products have not been authorized for use, and any company, organization, or individual who infringes the Company's patent rights through improper means will be subject to all possible legal actions taken by the Company to curb the infringement and to recover any damages suffered by the Company as a result of the infringement or any illegal benefits obtained by the infringer.

- \*The name and logo of Cmsemicon are registered trademarks of the Company.

- \*The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not authorized for use as critical components in lifesaving, lifesustaining devices or systems. The Company reserves the right to modify the products without prior notice. For the latest information, please visit the official website at www.mcu.com.cn.

## **Table of Contents**

| 1. P | PRODUCT DESCRIPTION                        | ε            |

|------|--------------------------------------------|--------------|

| 1.1  | FEATURES                                   | 6            |

| 1.2  | PRODUCT MODEL LIST                         | <del>7</del> |

| 1.3  | SYSTEM STRUCTURE DIAGRAM                   | 8            |

| 1.4  | Top view                                   | 9            |

| 1.   | .4.1 SC8F072AD606ST                        | 9            |

| 1.   | .4.2 SC8F072AD608SP                        |              |

| 1.   | .4.3 SC8F072AD610SP                        |              |

|      | .4.4 SC8F072AD614SP                        |              |

|      | .4.5 SC8F072AD616SP                        |              |

|      | .4.6 SC8F072AD616NPR                       |              |

| 1.5  | SYSTEM CONFIGURATION REGISTER              |              |

| 1.6  | ONLINE SERIAL PROGRAMMING                  |              |

| 1.7  | INTEGRATED DEVELOPMENT ENVIRONMENT         |              |

| 2. C | ENTRAL PROCESSING UNIT (CPU)               | 16           |

| 2.1  | Memory                                     |              |

|      | .1.1 Program memory                        |              |

|      | .1.2 Data memory                           |              |

| 2.2  | ADDRESSING MODE                            |              |

|      | .2.1 Direct addressing                     |              |

|      | .2.2 Immediate addressing                  |              |

|      | .2.3 Indirect addressing                   |              |

| 2.3  | STACK                                      |              |

| 2.4  | ACCUMULATOR (ACC)                          |              |

|      | .4.1 Overview                              |              |

| 2.5  | Program Status register (STATUS)           |              |

| 2.6  | Pre-scaler (OPTION_REG)                    |              |

| 2.7  | Program counter (PC)                       |              |

| 2.8  | WATCHDOG TIMER (WDT)                       |              |

|      | .8.1 WDT period                            |              |

|      | .8.2 Registers related to watchdog control |              |

| 3. S | SYSTEM CLOCK                               | 31           |

| 3.1  | Overview                                   |              |

| 3.2  | SYSTEM OSCILLATOR                          |              |

|      | .2.1 Internal RC oscillation               |              |

| 3.3  | Reset time                                 |              |

| 3.4  | OSCILLATOR CONTROL REGISTER                |              |

| 3.5  | CLOCK BLOCK DIAGRAM                        |              |

| 4. R | RESET                                      | 35           |

| 4.1  | Power on reset                             | 35           |

| 4.2  | EXTERNAL RESET                             |              |

| 4.3  | Power off reset                            |              |

|      | .3.1 Overview                              |              |

| 4.   | .3.2 Improvements for power off reset      |              |

| 4.4  | WATCHDOG RESET                             |              |

| 5. S | SLEEP MODE                                 | 40           |

| 5.1  | ENTER SLEEP MODE                           |              |

| 5.2  | Wake up from sleep mode                    |              |

| 5.3  | Interrupt wakeup                           |              |

| 5.4  | SLEEP MODE APPLICATION                     |              |

|      |                                            |              |

| 5.5          | WAKE-UP TIME IN SLEEP MODE                     | 42 |

|--------------|------------------------------------------------|----|

| 6. I/C       | D PORTS                                        | 43 |

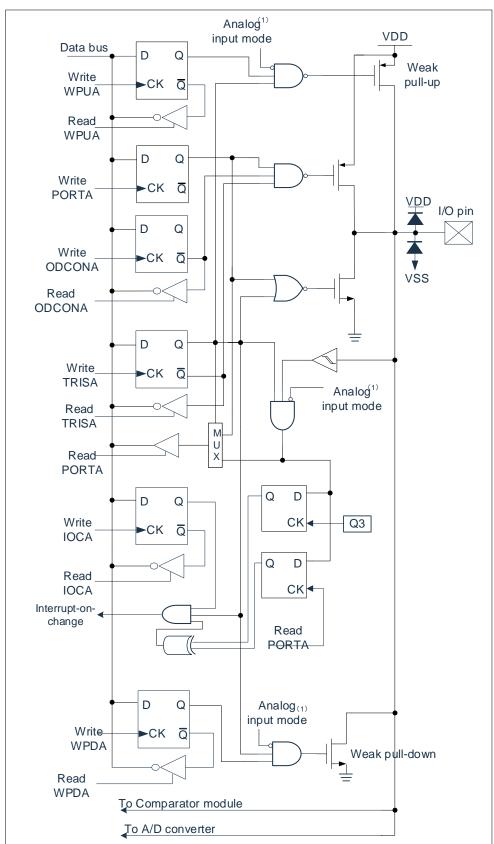

| 6.1          | I/O PORT STRUCTURE                             | 44 |

| 6.1          | 1.1 PORTA I/O port structure                   | 44 |

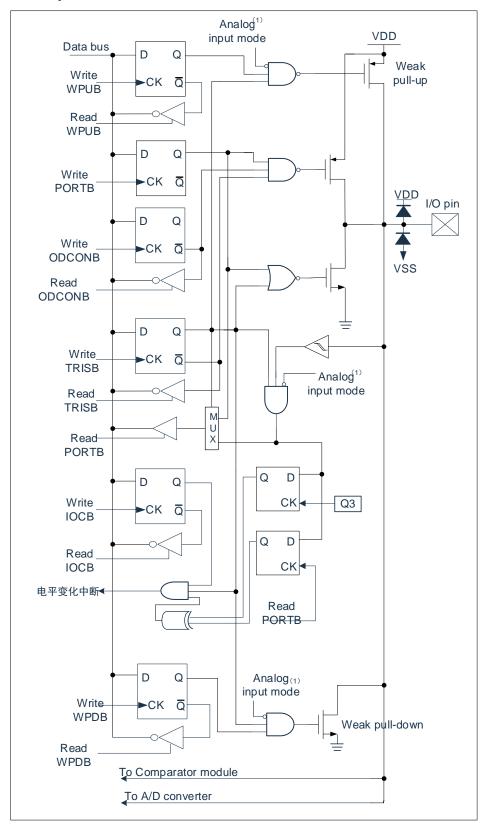

| 6.1          | 1.2 PORTB I/O port structure                   | 45 |

| 6.2          | PORTA                                          | 46 |

| 6.2          | 2.1 PORTA data and direction                   | 46 |

| 6.2          | 2.2 PORTA open-drain output control            | 47 |

| 6.2          | 2.3 PORTA analog select control                | 47 |

| 6.2          | 2.4 PORTA pull-up resistor                     | 48 |

| 6.2          | ·                                              |    |

| 6.2          | · · ·                                          |    |

| 6.3          | PORTB                                          |    |

| 6.3          |                                                |    |

| 6.3          |                                                |    |

| 6.3          | · · · · · · · · · · · · · · · · · · ·          |    |

| 6.3          | • •                                            |    |

| 6.3          | ·                                              |    |

| 6.3          | 1 3                                            |    |

| 6.4          | I/O usage                                      |    |

| 6.4          |                                                |    |

| • • • •      | 4.2 Read from I/O port                         |    |

| 6.5          | Cautions on I/O port usage                     | 55 |

| 7. IN        | ITERRUPT                                       | 56 |

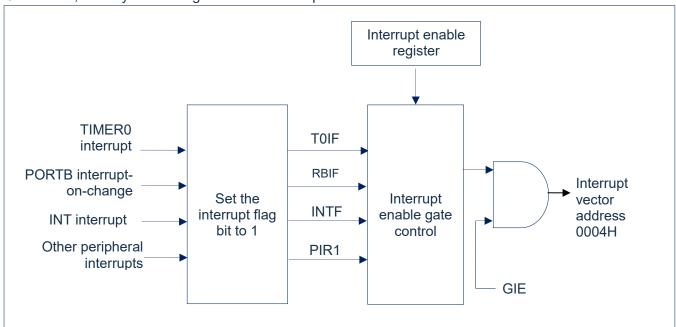

| 7.1          | Overview                                       | 56 |

| 7.2          | INTERRUPT CONTROL REGISTER                     |    |

|              | 2.1 Interrupt control register                 |    |

| 7.2          |                                                |    |

| 7.2          | 2.3 Peripheral interrupt request register      |    |

| 7.3          | PROTECTION METHODS FOR INTERRUPT               |    |

| 7.4          | INTERRUPT PRIORITY AND MULTI-INTERRUPT NESTING | 60 |

| R TII        | MER0                                           | 61 |

|              |                                                | _  |

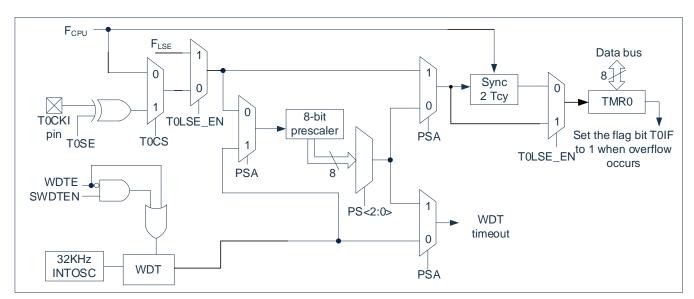

| 8.1          | TIMER0 overview                                |    |

| 8.2          | WORKING PRINCIPLE OF TIMER0                    |    |

| 8.2          |                                                |    |

| 8.2          |                                                |    |

| 8.2<br>8.2   |                                                |    |

| 8.2          | •                                              |    |

| 8.3          | TIMERO RELATED REGISTERS                       |    |

|              |                                                |    |

| 9. TII       | MER2                                           | 65 |

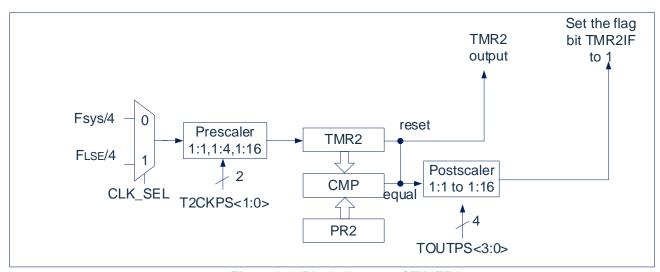

| 9.1          | TIMER2 OVERVIEW                                | 65 |

| 9.2          | Working principle of TIMER2                    | 66 |

| 9.3          | TIMER2 RELATED REGISTERS                       | 67 |

| 10. 10       | )-BIT PWM MODULE                               | 68 |

|              | PIN CONFIGURATION                              |    |

| 10.1<br>10.2 | PIN CONFIGURATION                              |    |

|              | 10-BIT PWM REGISTER WRITE SEQUENC              |    |

| 10.3<br>10.4 | 10-BIT PWM REGISTER WRITE SEQUENC              |    |

| 10.4         | 10-BIT PWM DUTY CYCLE                          |    |

| 10.5         | TU-BIT PWIM DUTY CYCLE                         |    |

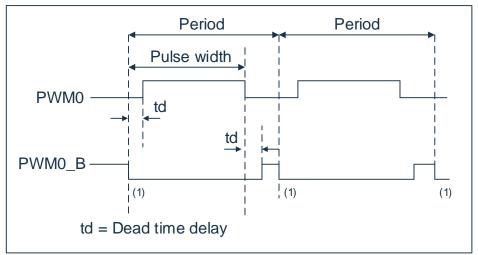

| 10.6         | PROGRAMMABLE DEAD TIME DELAY MODE              |    |

| 10.7         | I NOGRAMIMADLE DEAD TIME DELAT MODE            |    |

| 10.8         | 10-BIT PWM CONFIGURATION                                | /4  |

|--------------|---------------------------------------------------------|-----|

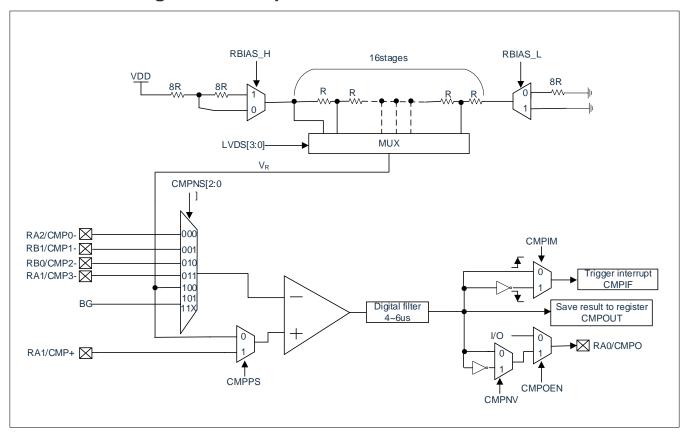

| 11. CC       | OMPARATOR (COMP)                                        | 75  |

| 11.1         | BLOCK DIAGRAM OF COMPARATOR FUNCTION                    | 75  |

| 11.2         | FEATURES                                                |     |

| 11.3         | COMPARATOR RELATED FUNCTIONS                            | 76  |

|              | 3.1 Comparator function description                     |     |

|              | 3.2 Comparator internal resistor voltage divider output |     |

|              | 3.3 Comparator for monitoring power supply voltage      |     |

|              | 3.4 Comparator interrupt usage                          |     |

|              | 3.5 Comparator interrupt sleep wake-up                  |     |

|              | 3.6 Comparator result output pin configuration          |     |

| 11.4         | RELATED REGISTERS                                       |     |

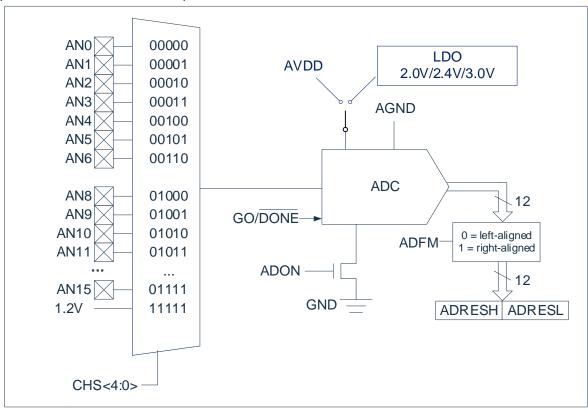

| 12. AN       | NALOG TO DIGITAL CONVERSION (ADC)                       |     |

| 12.1         | ADC overview                                            |     |

| 12.2         | ADC configuration                                       |     |

|              | 2.1 Port configuration                                  |     |

|              | 2.2 Channel selection                                   |     |

|              | 2.3 ADC internal base voltage                           |     |

|              | 2.4 ADC reference voltage                               |     |

|              | 2.5 Converter clock                                     |     |

|              | 2.6 ADC interrupt                                       |     |

|              | 2.7 Output formatting                                   |     |

| 12.3         |                                                         |     |

|              | 3.1 Start conversion                                    |     |

|              | 3.2 Complete conversion                                 |     |

|              | 3.4 Working principle of ADC in sleep mode              |     |

|              | 3.5 A/D conversion procedure                            |     |

|              | ADC RELATED REGISTERS                                   |     |

|              | ROGRAM EEPROM AND PROGRAM MEMORY CONTROL                |     |

|              | OVERVIEW                                                |     |

| 13.1<br>13.2 | OVERVIEW                                                |     |

|              | 2.1 EEADR and EEADRH registers                          |     |

|              | 2.2 EECON1 and EECON2 registers                         |     |

| 13.3         | READ PROGRAM EEPROM                                     |     |

| 13.4         | WRITE PROGRAM EEPROM                                    |     |

| 13.5         | READ PROGRAM MEMORY                                     |     |

| 13.6         | WRITE PROGRAM MEMORY                                    |     |

| 13.7         | CAUTIONS ON PROGRAM EEPROM                              |     |

| 13.          | .7.1 Program EEPROM programming time                    |     |

|              | 7.2 Write check                                         |     |

| 13.          | 7.3 Miswrite protection                                 | 95  |

| 14. EL       | ECTRICAL PARAMETERS                                     | 96  |

| 14.1         | LIMIT PARAMETERS                                        | 96  |

| 14.2         | DC characteristics                                      |     |

| 14.3         | COMPARATOR CHARACTERISTICS                              |     |

| 14.4         | ADC ELECTRICAL CHARACTERISTICS                          |     |

| 14.5         | Power on reset characteristics                          |     |

| 14.6         | AC ELECTRICAL CHARACTERISTICS                           |     |

| 14.7         | LSE CHARACTERISTICS                                     | 100 |

| 14.8         | EMC CHARACTERISTICS                                     | 101 |

| 14.          | 8.1 EFT electrical characteristics                      | 101 |

| 14.          | 8.2 ESD electrical characteristics                      | 101 |

|              |                                                         |     |

| 14.    | .8.3 Latch-Up electrical characteristics | 101 |

|--------|------------------------------------------|-----|

| 15. IN | STRUCTIONS                               | 102 |

|        | Instruction set                          |     |

|        | INSTRUCTION DESCRIPTION                  |     |

| 16. PA | ACKAGE                                   | 119 |

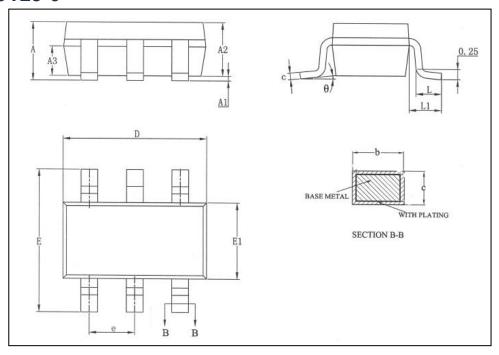

|        | SOT23-6                                  |     |

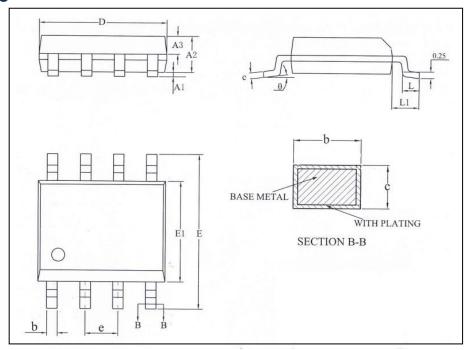

| 16.2   | SOP8                                     | 120 |

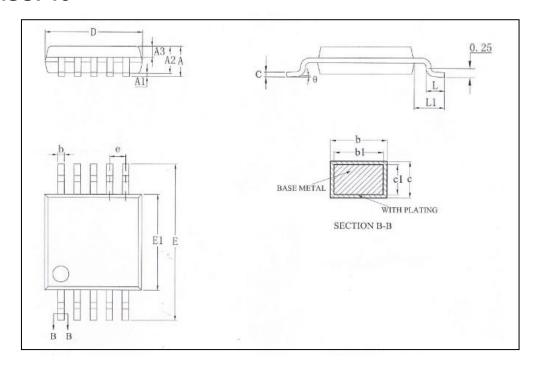

| 16.3   | MSOP10                                   | 121 |

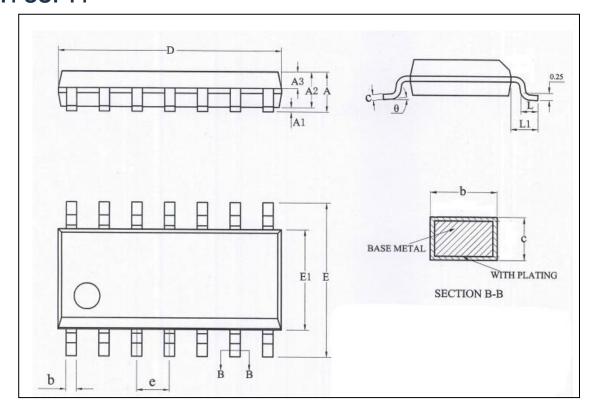

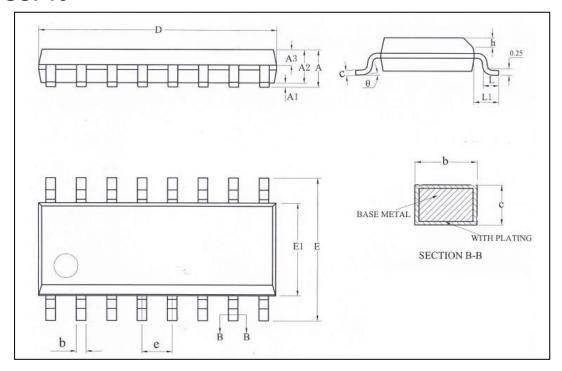

| 16.4   | SOP14                                    | 122 |

| 16.5   | SOP16                                    | 123 |

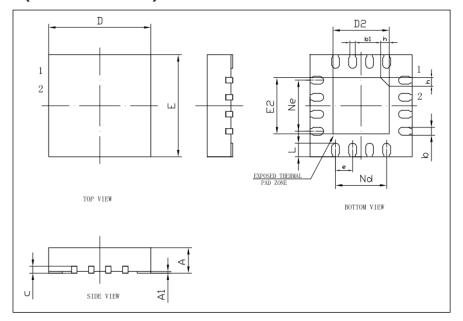

| 16.6   | QFN16(3*3*0.75-0.50)                     | 124 |

| 17. RE | EVISION HISTORY                          | 125 |

|        |                                          |     |

## 1. Product Description

### 1.1 Features

Memory

- MTP: 2K×16Bit

Universal RAM: 176×8Bit

- 8-level stack buffer

- Short and clear instruction system (66 instructions)

- Built-in low voltage detection circuit

- Built-in WDT

- ◆ Interrupt sources

- 2 timer interrupts

- RA, RB ports interrupt on change

- Other peripheral interrupts

- ◆ Built-in 128-byte EEPROM

- 10,000 times rewritable

- Timer

- 8-bit timers: TIMER0. TIMER2

- TIMER0, TIMER2 can select external 32.768Khz oscillating clock source

- ♦ Built-in comparator module

- Positive: RA1/resistor divider outputs

- Negative: RA1/RA2/RB0/RB1/BG/resistor divider outputs

- Operating voltage: VLVR3 to 5.5V@16MHz/2T VLVR1 to 5.5V@16MHz/4T

- Operating temperature: -40°C to 85°C

- Internal RC oscillation: designed frequency of 16MHz

- Instruction period (single instruction or dual instruction)

- ◆ Built-in PWM module

- 5-channel PWM with 2-channel complementary output and selectable polarity

- 4-channel PWM common period, independent duty cycle

- 1-channel PWM independent period, independent duty cycle

- 10-bit PWM accuracy

- ◆ LVR can be selected from 1.8V/2V/2.5V/3V

- ♦ High accuracy 12-bit ADC

- Built-in high accuracy 1.2V reference voltage

- Optional internal reference sources: 2.0V/2.4V/3.0V

### 1.2 Product model list

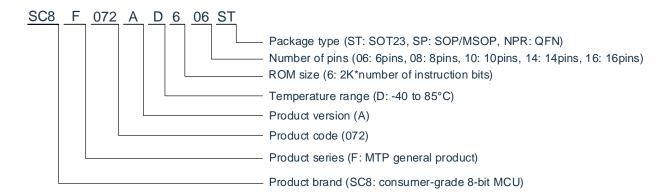

### Model description

| PRODUCT         | ROM   | RAM   | Pro EE | PWM | ACOMP | I/O | ADC      | TIMER | PACKAGE |

|-----------------|-------|-------|--------|-----|-------|-----|----------|-------|---------|

| SC8F072AD606ST  | 2K×16 | 176×8 | 128×16 | 3   | 1     | 4   | 12Bit×4  | 2     | SOT23-6 |

| SC8F072AD608SP  | 2K×16 | 176×8 | 128×16 | 5   | 1     | 6   | 12Bit×6  | 2     | SOP8    |

| SC8F072AD610SP  | 2K×16 | 176×8 | 128×16 | 5   | 1     | 8   | 12Bit×8  | 2     | MSOP10  |

| SC8F072AD614SP  | 2K×16 | 176×8 | 128×16 | 5   | 1     | 12  | 12Bit×12 | 2     | SOP14   |

| SC8F072AD616SP  | 2K×16 | 176×8 | 128×16 | 5   | 1     | 14  | 12Bit×14 | 2     | SOP16   |

| SC8F072AD616NPR | 2K×16 | 176×8 | 128×16 | 5   | 1     | 14  | 12Bit×14 | 2     | QFN16   |

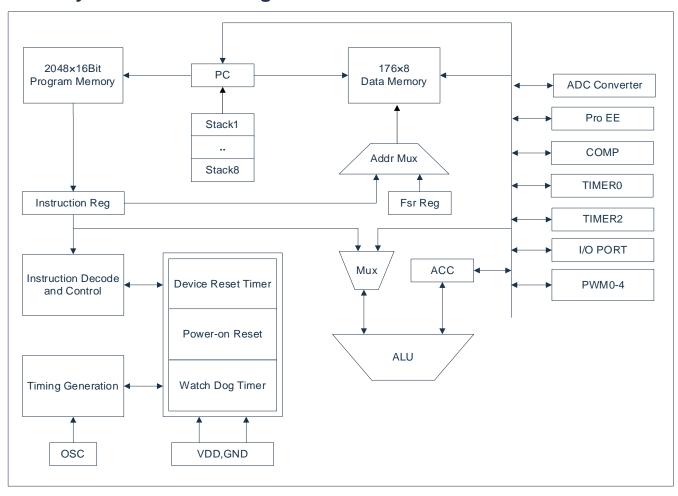

## 1.3 System structure diagram

## 1.4 Top view

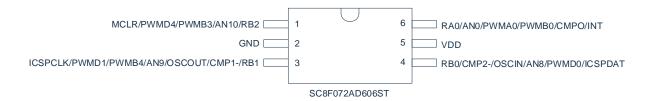

### 1.4.1 SC8F072AD606ST

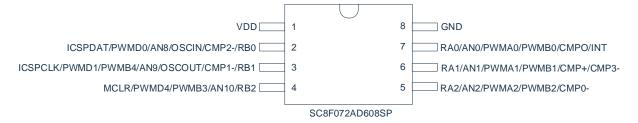

#### 1.4.2 SC8F072AD608SP

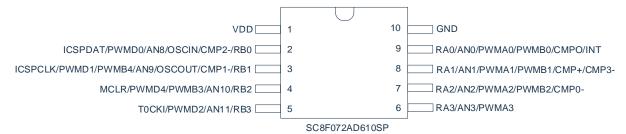

### 1.4.3 SC8F072AD610SP

www.mcu.com.cn 9 / 125 V1.0.5

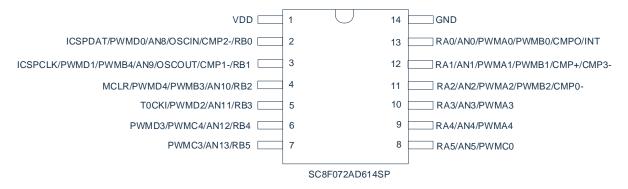

### 1.4.4 SC8F072AD614SP

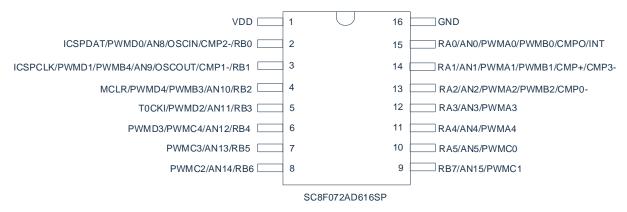

### 1.4.5 SC8F072AD616SP

www.mcu.com.cn 10 / 125 V1.0.5

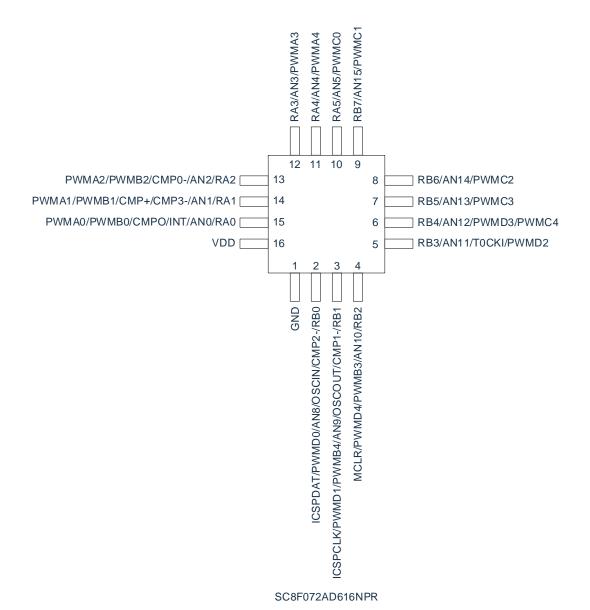

### 1.4.6 SC8F072AD616NPR

### SC8F072 pin description:

| Pin name                   | IO type | Pin description                                                                                                                                     |

|----------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD,GND                    | Р       | Supply voltage input pin, ground pin                                                                                                                |

| RA0-RA5                    | I/O     | Programmable as input pin, push-pull or open-drain output pin, with pull-up and pull-down resistor functionality, and interrupt-on-change function. |

| RB0-RB7                    | I/O     | Programmable as input pin, push-pull or open-drain output pin, with pull-up and pull-down resistor functionality, and interrupt-on-change function. |

| ICSPCLK/ICSPDAT            | I/O     | Programmable clock/data pin                                                                                                                         |

| PWMA0-PWMA4                | 0       | PWM output pin                                                                                                                                      |

| PWMB0-PWMB4                | 0       | PWM output pin                                                                                                                                      |

| PWMC0-PWMC4                | 0       | PWM output pin                                                                                                                                      |

| PWMD0-PWMD4                | 0       | PWM output pin                                                                                                                                      |

| AN0-AN5, AN8-AN15          | 1       | 12-bit ADC input pin                                                                                                                                |

| INT                        | 1       | External interrupt input pin                                                                                                                        |

| CMP+                       | 1       | Comparator positive input pin                                                                                                                       |

| CMP0-, CMP1-, CMP2-, CMP3- | 1       | Comparator negative input pin                                                                                                                       |

| CMPO                       | 0       | Comparator result output pin                                                                                                                        |

| T0CKI                      | 1       | TIMER0 external clock input pin                                                                                                                     |

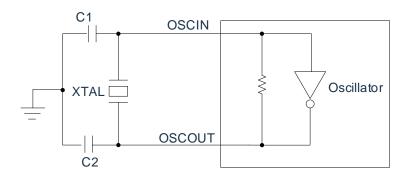

| OSCIN/OSCOUT               | I/O     | 32.768K crystal oscillator input pin/output pin                                                                                                     |

| MCLR                       | 1       | External reset input pin                                                                                                                            |

## 1.5 System configuration register

The System Configuration Register (CONFIG) is a FLASH option for the initial condition of the MCU. It can only be written by the SC programmer and cannot be accessed or manipulated by the user. It contains the following contents.

- 1. WDT (watchdog selection)

- ENABLE Enable WDT

- DISABLE Disable WDT

- 2. PROTECT (encrypted)

- DISABLE ROM code is not encrypted

- ◆ ENABLE ROM code is encrypted, and the value read out by the programmed emulator will be uncertain after encryption

- 3. LVR SEL (low-voltage detection selection)

- ♠ 1.8V

- ◆ 2.0V

- 2.5V

- ◆ 3.0V

- 4. F<sub>CPU</sub> DIV (instruction clock divison)

- ◆ 4T Divided by 4, F<sub>CPU</sub>=F<sub>SYS</sub>/4

- ◆ 2T Divided by 2, F<sub>CPU</sub>=F<sub>SYS</sub>/2

- 5. ICSPPORT SEL (Emulation port function selection)

- The ICSPCLK and DAT ports remain as emulation ports, and all functions cannot be used.

- NORMAL ICSPCLK, DAT ports are general function ports

- 6. EXT RESET (external reset port selection)

- DISABLE Disable external reset function, RB2 is used as a normal IO port.

- ENABLE Enable external reset function, RB2 is used as an external reset port.

## 1.6 Online serial programming

The microcontroller can be programmed serially in the final application circuit. Programming can be done simply with the following 4 wires.

- Power wire

- Ground wire

- Data wire

- Clock wire

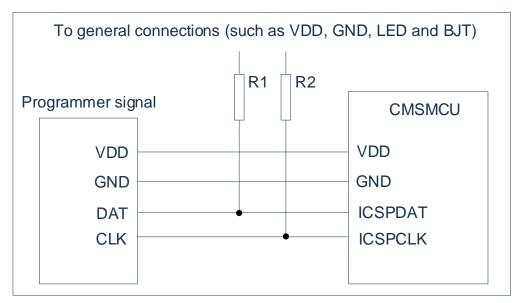

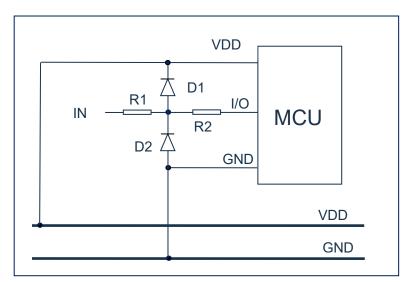

Figure 1-1: Typical connection for online serial programming

In the above figure, R1 and R2 are the electrical isolation devices, normally represented by resistors with the following resistance values:  $R1 \ge 4.7K$ ,  $R2 \ge 4.7K$ .

## 1.7 Integrated development environment

- On-Chip Debug (OCD), ISP

- 4 hardware breakpoints

- Software reset, pause, single step, run, etc.

# 2. Central Processing Unit (CPU)

### 2.1 Memory

### 2.1.1 Program memory

SC8F072 program memory space

FLASH: 2K

| 0000H | Reset vector               | Program start, jump to user program |

|-------|----------------------------|-------------------------------------|

| 0001H |                            | program                             |

| 0002H |                            |                                     |

| 0003H |                            |                                     |

| 0004H | Interrupt vector           |                                     |

| •••   |                            | User program region                 |

|       |                            |                                     |

|       |                            |                                     |

| 07FDH |                            |                                     |

| 07FEH |                            |                                     |

| 07FFH | Jump to reset vector 0000H | Program end                         |

| ļ     |                            |                                     |

### 2.1.1.1 Reset vector (0000H)

The MCU has a 1-byte long system reset vector (0000H). It has 3 ways to reset:

- ◆ Power-on reset

- Watchdog reset

- ◆ Low Voltage Reset (LVR)

After any of the above resets, program execution will restart from 0000H and the system registers will be restored to their default values. The system reset mode can be determined by the PD and TO flags of the STATUS register. The following program demonstrates how to define a reset vector in FLASH.

Example: define a reset vector

|        | ORG<br>JP | 0000H<br>START | ;system reset vector |

|--------|-----------|----------------|----------------------|

| CTADT. | ORG       | 0010H          | ;program start       |

| START: |           |                | ;user program        |

|        | •••       |                |                      |

|        | END       |                | ;program end         |

### 2.1.1.2Interrupt vector

The address for interrupt vector is 0004H. Once the interrupt responds, the current value for program counter (PC) will be saved to stack buffer and jump to 0004H to execute interrupt service program. All interrupt will enter 0004H. Users will determine which interrupt to execute according to the bit of the interrupt request flag bit register. The following program illustrates how to write interrupt service program.

Example: Define an interrupt vector, and the interrupt program is placed after the user program.

|            | ORG  | 0000H | ;system reset vector    |

|------------|------|-------|-------------------------|

|            | JP   | START |                         |

|            | ORG  | 0004H | ;user program start     |

| INT_START: |      |       |                         |

|            | CALL | PUSH  | ;save ACC and STATUS    |

|            |      |       | ;user interrupt program |

|            |      |       |                         |

| INT_BACK:  |      |       |                         |

|            | CALL | POP   | ;back to ACC and STATUS |

|            | RETI |       | ;interrupt back         |

| START:     |      |       |                         |

|            |      |       | ;user program           |

|            |      |       |                         |

|            | END  |       | ;program end            |

Note: Since the microcontroller does not provide specific instructions for stack operations, users need to protect the interrupt context themselves.

Example: interrupt-in protection

| PUSH: |       |              |                           |

|-------|-------|--------------|---------------------------|

|       | LD    | ACC_BAK,A    | ;save ACC to ACC_BAK      |

|       | SWAPA | STATUS       | ;swap half-byte of STATUS |

|       | LD    | STATUS_BAK,A | ;save to STATUS_BAK       |

|       | RET   |              | ;back                     |

Example: interrupt-out restore

| POP: |       |            |                                                 |

|------|-------|------------|-------------------------------------------------|

|      | SWAPA | STATUS_BAK | ;swap the half-byte data from STATUS_BAK to ACC |

|      | LD    | STATUS,A   | ;pass the value in ACC to STATUS                |

|      | SWAPR | ACC_BAK    | ;swap the half-byte data in ACC_BAK             |

|      | SWAPA | ACC_BAK    | ;swap the half-byte data from ACC_BAK to ACC    |

|      | RET   |            | ;back                                           |

### 2.1.1.3 Jump table

The jump table enables multiple address jumps. Since the PCL and ACC values can be added together to get a new PCL, multiple address jumps can be realized by adding different ACC values to the PCL. If the value of ACC is n, then PCL+ACC represents the current address plus n. After the execution of the current instructions, the value of PCL will add 1 (refer to the following examples). If PCL+ACC overflows, then PC will not carry. As such, users can achieve multi-address jumps by changing the value of ACC.

PCLATH is the PC high buffer register and must be assigned first when operating on the PCL.

Example: correct multi-address jump

|               |      | =        |                       |  |

|---------------|------|----------|-----------------------|--|

| FLASH address |      |          |                       |  |

|               | LDIA | 01H      |                       |  |

|               | LD   | PCLATH,A | ;load value to PCLATH |  |

|               |      |          |                       |  |

| 0110H:        | ADDR | PCL      | ;ACC+PCL              |  |

| 0111H:        | JP   | LOOP1    | ;ACC=0, jump to LOOP1 |  |

| 0112H:        | JP   | LOOP2    | ;ACC=1, jump to LOOP2 |  |

| 0113H:        | JP   | LOOP3    | ;ACC=2, jump to LOOP3 |  |

| 0114H:        | JP   | LOOP4    | ;ACC=3, jump to LOOP4 |  |

| 0115H:        | JP   | LOOP5    | ;ACC=4, jump to LOOP5 |  |

| 0116H:        | JP   | LOOP6    | ;ACC=5, jump to LOOP6 |  |

Example: wrong multi-address jump

| FLASH address |      |        |                               |

|---------------|------|--------|-------------------------------|

|               | CLR  | PCLATH |                               |

|               |      |        |                               |

| 00FCH:        | ADDR | PCL    | ;ACC+PCL                      |

| 00FDH:        | JP   | LOOP1  | ;ACC=0, jump to LOOP1         |

| 00FEH:        | JP   | LOOP2  | ;ACC=1, jump to LOOP2         |

| 00FFH:        | JP   | LOOP3  | ;ACC=2, jump to LOOP3         |

| 0100H:        | JP   | LOOP4  | ;ACC=3, jump to address 0000H |

| 0101H:        | JP   | LOOP5  | ;ACC=4, jump to address 0001H |

| 0102H:        | JP   | LOOP6  | ;ACC=5, jump to address 0002H |

Note: Since PCL overflow does not automatically carry into the high byte, when using PCL for multiple-address jumps, it is important to ensure that this section of code is not placed at the boundary of FLASH memory pages.

## 2.1.2 Data memory

### SC8F072 data memory list

|                               | Add. |                               | Add. |       | Add. |       | Ad  |

|-------------------------------|------|-------------------------------|------|-------|------|-------|-----|

| INDF                          | 00H  | INDF                          | 80H  |       | 100H |       | 180 |

| OPTION_REG                    | 01H  | TMR0                          | 81H  |       | 101H |       | 18  |

| PCL                           | 02H  | PCL                           | 82H  |       | 102H |       | 18  |

| STATUS                        | 03H  | STATUS                        | 83H  |       | 103H |       | 18  |

| FSR                           | 04H  | FSR                           | 84H  |       | 104H |       | 18  |

| TRISB                         | 05H  | TRISA                         | 85H  |       | 105H |       | 18  |

| PORTB                         | 06H  | PORTA                         | 86H  |       | 106H |       | 18  |

| WPDB                          | 07H  | WPDA                          | 87H  |       | 107H |       | 18  |

| WPUB                          | 08H  | WPUA                          | 88H  |       | 108H |       | 18  |

| IOCB                          | 09H  | IOCA                          | 89H  |       | 109H |       | 18  |

| PCLATH                        | 0AH  | PCLATH                        | 8AH  |       | 10AH |       | 18/ |

| INTCON                        | 0BH  | INTCON                        | 8BH  |       | 10BH |       | 181 |

| ODCONB                        | 0CH  | ODCONA                        | 8CH  |       | 10CH |       | 180 |

| PIR1                          | 0DH  | EECON1                        | 8DH  |       | 10DH |       | 18[ |

| PIE1                          | 0EH  | EECON2                        | 8EH  |       | 10EH |       | 181 |

| CMPCON0                       | 0FH  | EEDAT                         | 8FH  |       | 10FH |       | 181 |

| CMPCON1                       | 10H  | EEDATH                        | 90H  |       | 110H |       | 190 |

| PR2                           | 11H  | EEADR                         | 91H  |       | 111H |       | 19  |

| TMR2                          | 12H  | EEADRH                        | 92H  |       | 112H |       | 19  |

| T2CON                         | 13H  | ANSEL0                        | 93H  |       | 113H |       | 19  |

| OSCCON                        | 14H  | ANSEL1                        | 94H  |       | 114H |       | 19  |

| PWMCON0                       | 15H  | ADCON0                        | 95H  |       | 115H |       | 19  |

| PWMCON1                       | 16H  | ADCON1                        | 96H  |       | 116H |       | 190 |

| PWMTL                         | 17H  |                               | 97H  |       | 117H |       | 19  |

| PWMTH                         | 18H  | ADRESL                        | 98H  |       | 118H |       | 198 |

| PWMD0L                        | 19H  | ADRESH                        | 99H  |       | 119H |       | 19  |

| PWMD1L                        | 1AH  |                               | 9AH  |       | 11AH |       | 19  |

| PWMD4L                        | 1BH  | PWMD2L                        | 9BH  |       | 11BH |       | 191 |

| PWMT4L                        | 1CH  | PWMD3L                        | 9CH  |       | 11CH |       | 190 |

| PWMCON2                       | 1DH  | PWM23DT                       | 9DH  |       | 11DH |       | 191 |

| PWMD01H                       | 1EH  | PWMD23H                       | 9EH  |       | 11EH |       | 191 |

| PWM01DT                       | 1FH  |                               | 9FH  |       | 11FH |       | 191 |

|                               | 20H  |                               | A0H  |       | 120H |       | 1A  |

| Universal register<br>96-byte |      | Universal register<br>80-byte | BFH  |       |      |       |     |

| ĺ                             |      |                               |      |       |      |       |     |

|                               |      |                               | EFH  |       | 16FH |       | 1E  |

|                               |      | Rapid storage area            | F0H  |       | 170H |       | 1F  |

|                               |      | 70H-7FH                       |      |       |      |       | -   |

|                               | 7FH  |                               | FFH  |       | 17FH |       | 1F  |

| BANK0                         |      | BANK1                         |      | BANK2 |      | BANK3 |     |

Data memory is divided into two functional areas: special function registers and universal data memory. Most of the data memory cells are readable/writable, but some are read-only. Special function registers are addressed from 00H to 1FH, 80 to 9FH.

### SC8F072 special function register summary Bank0

| Add. | Name       | Bit7     | Bit6                       | Bit5            | Bit4              | Bit3                                                    | Bit      | t2               | Bit1                 | Bit0           | Reset value |

|------|------------|----------|----------------------------|-----------------|-------------------|---------------------------------------------------------|----------|------------------|----------------------|----------------|-------------|

| 00H  | INDF       | Ad       | Idressing this             | unit will addre | ss data memory (r | not a physical register) using the contents of the FSR. |          |                  |                      |                | xxxxxxx     |

| 01H  | OPTION_REG | T0LSE_EN | INTEDG                     | T0CS            | S TOSE PSA        |                                                         |          | S2               | PS1                  | PS0            | 01111011    |

| 02H  | PCL        |          |                            |                 | Program c         | counter low byte                                        |          |                  |                      | T              | 00000000    |

| 03H  | STATUS     | IRP      | RP1                        | RP0             | ТО                | PD                                                      | Z        | 7                | DC                   | С              | 00011xxx    |

| 04H  | FSR        |          |                            |                 | Indirect data me  | mory address po                                         | ointer   | •                | xxxxxxx              |                |             |

| 05H  | TRISB      | TRISB7   | TRISB6                     | TRISB5          | TRISB4            | TRISB3                                                  | TRIS     | SB2              | TRISB1               | TRISB0         | 11111111    |

| 06H  | PORTB      | RB7      | RB6                        | RB5             | RB4               | RB3                                                     | RE       | B2               | RB1                  | RB0            | xxxxxxx     |

| 07H  | WPDB       | WPDB7    | WPDB6                      | WPDB5           | WPDB4             | WPDB3                                                   | WPE      | DB2              | WPDB1                | WPDB0          | 0000-000    |

| 08H  | WPUB       | WPUB7    | WPUB6                      | WPUB5           | WPUB4             | WPUB3                                                   | WPU      | UB2              | WPUB1                | WPUB0          | 00000000    |

| 09H  | IOCB       | IOCB7    | IOCB6                      | IOCB5           | IOCB4             | IOCB3                                                   | IOC      | CB2              | IOCB1                | IOCB0          | 00000000    |

| 0AH  | PCLATH     |          |                            |                 |                   |                                                         | Write    | e buffer for the | high 3 bits of the p | rogram counter | 000         |

| 0BH  | INTCON     | GIE      | PEIE                       | T0IE            | INTE              | RBIE                                                    | T0       | )IF              | INTF                 | RBIF           | 00000000    |

| 0CH  | ODCONB     | ODCONB7  | ODCONB                     | ODCONB          | ODCONB4           | ODCONB3                                                 | ODCC     | ONB2             | ODCONB1              | ODCONB0        | 00000000    |

|      |            |          | 6                          | 5               |                   |                                                         |          |                  |                      |                |             |

| 0DH  | PIR1       |          |                            | CMPIF           | PWMIF             | RAIF                                                    |          |                  | TMR2IF               | ADIF           | 000-00      |

| 0EH  | PIE1       |          |                            | CMPIE           | PWMIE             | RAIE                                                    |          |                  | TMR2IE               | ADIE           | 000-00      |

| 0FH  | CMPCON0    | CMPEN    | CMPPS                      | CMPNS2          | CMPNS1            | CMPNS0                                                  | CMF      | PNV              | CMPOUT               | CMPOEN         | 00000000    |

| 10H  | CMPCON1    | CMPIM    | AN_EN                      | RBIAS_H         | RBIAS_L           |                                                         |          | LVDS<            | 3:0>                 | 00000000       |             |

| 11H  | PR2        |          |                            |                 | TIMER2            | period register                                         |          |                  |                      |                | 11111111    |

| 12H  | TMR2       |          |                            |                 | TIMER2 r          | module register                                         |          |                  |                      |                | 00000000    |

| 13H  | T2CON      | CLK_SEL  | TOUTPS3                    | TOUTPS2         | TOUTPS1           | TOUTPS0                                                 | -        | TMR2ON           | T2CKPS1              | T2CKPS0        | 00000000    |

| 14H  | OSCCON     |          | IRCF2                      | IRCF1           | IRCF0             |                                                         |          |                  | SWDTEN               |                | -1011-      |

| 15H  | PWMCON0    | C        | CLKDIV<2:0>                |                 | PWM4EN            | PWM3EN                                                  | F        | PWM2EN           | PWM1EN               | PWM0EN         | 00000000    |

| 16H  | DWMOONIA   | PWMIO_S  | SEL[1:0]                   | PWM2DT          | PWM0DTEN          |                                                         |          |                  | DT_D                 | IV<1:0>        | 000000      |

|      | PWMCON1    |          |                            | EN              |                   |                                                         |          |                  |                      |                |             |

| 17H  | PWMTL      |          |                            | 1               | PWM0 to PWM3 p    | eriod low 8-bit re                                      | egisters |                  |                      |                | 00000000    |

| 18H  | PWMTH      |          |                            | P               | WM4D<9:8>         | P                                                       | WM4T<9   | 9:8>             | PWM                  | IT<9:8>        | 000000      |

| 19H  | PWMD0L     |          |                            |                 | PWM0 duty         | cycle low 8 bits                                        | 5        |                  |                      |                | 00000000    |

| 1AH  | PWMD1L     |          | PWM1 duty cycle low 8 bits |                 |                   |                                                         |          |                  | 00000000             |                |             |

| 1BH  | PWMD4L     |          |                            |                 | PWM4 duty         | / cycle low 8 bits                                      | ;        |                  |                      |                | 00000000    |

| 1CH  | PWMT4L     |          |                            |                 | PWM4 period       | d low 8-bit regist                                      | er       |                  |                      |                | 00000000    |

| 1DH  | PWMCON2    |          |                            |                 | PWM4DIR           | PWM3DIR                                                 | PWM:     | 12DIR            | PWM1DIR              | PWM0DIR        | 00000       |

| 1EH  | PWMD01H    |          |                            | PWN             | 1D1<9:8>          |                                                         |          |                  | PWMD0                | )<9:8>         | 0000        |

| 1FH  | PWM01DT    |          |                            |                 |                   | PWM0                                                    | 1DT<5:0: | )>               |                      |                | 000000      |

### SC8F072 special function register summary Bank1

|      |          |                 |                                                                                                        |         | ,                     |                    |                   |                   |             |             |

|------|----------|-----------------|--------------------------------------------------------------------------------------------------------|---------|-----------------------|--------------------|-------------------|-------------------|-------------|-------------|

| Add. | Name     | Bit7            | Bit6                                                                                                   | Bit5    | Bit4                  | Bit3               | Bit2              | Bit1              | Bit0        | Reset value |

| 80H  | INDF     | Add             | Addressing this unit will address data memory (not a physical register) using the contents of the FSR. |         |                       |                    |                   |                   |             | xxxxxxx     |

| 81H  | TMR0     |                 |                                                                                                        |         | TIMER0                | data register      |                   |                   |             | xxxxxxx     |

| 82H  | PCL      |                 |                                                                                                        |         | Program co            | unter low byte     |                   |                   |             | 00000000    |

| 83H  | STATUS   | IRP             | RP1                                                                                                    | RP0     | ТО                    | PD                 | Z                 | DC                | С           | 00011xxx    |

| 84H  | FSR      |                 |                                                                                                        | Ir      | ndirect data men      | nory address poi   | nter              |                   |             | xxxxxxx     |

| 85H  | TRISA    |                 |                                                                                                        | TRISA5  | TRISA4                | TRISA3             | TRISA2            | TRISA1            | TRISA0      | 111111      |

| 86H  | PORTA    |                 |                                                                                                        | RA5     | RA4                   | RA3                | RA2               | RA1               | RA0         | xxxxxx      |

| 87H  | WPDA     |                 |                                                                                                        | WPDA5   | WPDA4                 | WPDA3              | WPDA2             | WPDA1             | WPDA0       | 000000      |

| 88H  | WPUA     |                 |                                                                                                        | WPUA5   | WPUA4                 | WPUA3              | WPUA2             | WPUA1             | WPUA0       | 000000      |

| 89H  | IOCA     |                 |                                                                                                        | IOCA5   | IOCA4                 | IOCA3              | IOCA2             | IOCA1             | IOCA0       | 000000      |

| 8AH  | PCLATH   |                 |                                                                                                        |         |                       |                    | Write buff        | er for the high 3 | bits of the | 000         |

|      |          | program counter |                                                                                                        |         |                       |                    |                   |                   | r           |             |

| 8BH  | INTCON   | GIE             | PEIE                                                                                                   | TOIE    | INTE                  | RBIE               | TOIF              | INTF              | RBIF        | 00000000    |

| 8CH  | ODCONA   |                 |                                                                                                        | ODCONA5 | ODCONA4               | ODCONA3            | ODCONA2           | ODCONA1           | ODCONA0     | 000000      |

| 8DH  | EECON1   | EEPGD           |                                                                                                        |         |                       | WRERR              | WREN              | WR                | RD          | 00000       |

| 8EH  | EECON2   |                 |                                                                                                        | EEPROI  | M control registe     | er 2 (not a physic | al register)      |                   |             |             |

| 8FH  | EEDAT    | EEDAT7          | EEDAT6                                                                                                 | EEDAT5  | EEDAT4                | EEDAT3             | EEDAT2            | EEDAT1            | EEDAT0      | xxxxxxx     |

| 90H  | EEDATH   | EEDATH7         | EEDATH                                                                                                 | EEDATH5 | EEDATH4               | EEDATH3            | 3 EEDATH2 EEDATH1 | EEDATH0           | xxxxxxx     |             |

|      | LLD/(III |                 | 6                                                                                                      |         |                       |                    |                   |                   |             |             |

| 91H  | EEADR    | EEADR7          | EEADR6                                                                                                 | EEADR5  | EEADR4                | EEADR3             | EEADR2            | EEADR1            | EEADR0      | 00000000    |

| 92H  | EEADRH   |                 |                                                                                                        |         |                       |                    | EEADRH2           | EEADRH1           | EEADRH0     | 000         |

| 93H  | ANSEL0   |                 |                                                                                                        | ANS5    | ANS4                  | ANS3               | ANS2              | ANS1              | ANS0        | 000000      |

| 94H  | ANSEL1   | ANS15           | ANS14                                                                                                  | ANS13   | ANS12                 | ANS11              | ANS10             | ANS9              | ANS8        | 00000000    |

| 95H  | ADCON0   | ADCS1           | ADCS0                                                                                                  | CHS3    | CHS2                  | CHS1               | CHS0              | GO/ DONE          | ADON        | 00000000    |

| 96H  | ADCON1   | ADFM            | CHS4                                                                                                   |         |                       |                    | LDO_EN            | LDO_SEL1          | LDO_SEL0    | 00000       |

| 98H  | ADRESL   |                 | Low byte of the A/D result register                                                                    |         |                       |                    |                   |                   | xxxxxxx     |             |

| 99H  | ADRESH   |                 | High byte of the A/D result register                                                                   |         |                       |                    |                   |                   | xxxxxxx     |             |

| 9BH  | PWMD2L   |                 |                                                                                                        |         | PWM2 duty             | cycle low 8 bits   |                   |                   |             | 00000000    |

| 9CH  | PWMD3L   |                 |                                                                                                        |         | PWM3 duty             | cycle low 8 bits   |                   |                   |             | 00000000    |

| 9DH  | PWM23DT  |                 |                                                                                                        |         |                       | PWM23 dead a       | one delay time    |                   |             | 000000      |

| 9EH  | PWMD23H  |                 |                                                                                                        | PWMD    | PWMD3<9:8> PWMD2<9:8> |                    |                   |                   |             | 0000        |

|      |          |                 |                                                                                                        |         |                       |                    |                   |                   |             |             |

## 2.2 Addressing mode

### 2.2.1 Direct addressing

It operates the RAM through the operation register (ACC).

Example: pass the value in ACC to 30H register

LD 30H,A

Example: pass the value in 30H register to ACC

LD A,30H

### 2.2.2 Immediate addressing

Pass the immediate value to accumulator (ACC)

Example: pass the immediate value 12H to ACC

LDIA 12H

### 2.2.3 Indirect addressing

The data memory can be addressed directly or indirectly. Direct addressing can be achieved through the INDF register, and the INDF is not a physical register. When the INDF is accessed, it is addressed according to the value in the FSR register, and points to the register at that address. Therefore, after setting the FSR register, the INDF register can be regarded as a target register. Reading the INDF (FSR=0) indirectly will produce a 00H. Write to the INDF register indirectly will cause a null operation. The following example shows how indirect addressing works.

Example: application of FSR and INDF

| LDIA | 30H   |                                                                          |

|------|-------|--------------------------------------------------------------------------|

| LD   | FSR,A | ;point to 30H for indirect addressing                                    |

| CLR  | INDF  | ;clear INDF, which means clearing the 30H address RAM that FSR points to |

### Example: clear RAM (20H-7FH) for indirect addressing

|       | LDIA | 1FH      |                                            |

|-------|------|----------|--------------------------------------------|

|       | LD   | FSR,A    | ;point to 1FH for indirect addressing      |

| LOOP: |      |          |                                            |

|       | INCR | FSR      | ;address add 1, and initial address is 20H |

|       | CLR  | INDF     | ;clear the address where FSR points to     |

|       | LDIA | 7FH      |                                            |

|       | SUBA | FSR      |                                            |

|       | SNZB | STATUS,C | ;clear until the address of FSR is 7FH     |

|       | JP   | LOOP     |                                            |

### 2.3 Stack

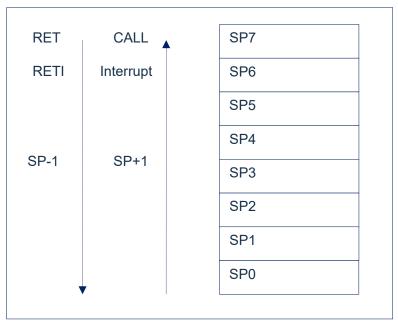

The stack buffer of the chip has 8 levels. The stack buffer is not part of data memory nor program memory, and it cannot be written nor read. It is operated by the stack pointer (SP) and cannot be read out or written in, the stack pointer will point to the top of the stack after system reset. When a subroutine call or an interrupt occurs, values in the program counter (PC) will be transferred to the stack buffer. When returning from an interruption or subroutine, the values are returned to the program counter (PC). Figure 2-2 illustrates how this works.

Figure 2-2: How the stack buffer works

Stack buffer will follow one principle: 'first in last out'.

Note: Stack buffer has only 8 levels, if the stack is full and an interrupt happens which is non-maskable, then only the flag bit of the interrupt will be logged. The response for the interrupt will be suppressed until the pointer of stack starts to decrease. This feature can prevent overflow of the stack caused by the interrupt. Similarly, when stack is full and subroutine happens, then stack will overflow and the contents which enter the stack first will be lost, only the last 8 return addresses will be saved. Therefore, users should pay attention to this point when writing programs to avoid program loops.

## 2.4 Accumulator (ACC)

#### 2.4.1 Overview

The ALU is an 8-bit arithmetic-logic unit. All math and logic related calculations in MCU are done by the ALU. It can perform addition, subtraction, shift and logical calculation on data; the ALU can also control STATUS to represent the status of the calculation result.

The ACC register is an 8-bit register where the ALU's operation results can be stored. It is not part of the data storage but is located in the CPU for the ALU to use in its operation, so it cannot be addressed and can only be used by the instructions provided.

### 2.4.2 ACC application

### Example: use ACC for data transferring

| LD | A,R01 | ;load the value in register R01 to ACC |

|----|-------|----------------------------------------|

| LD | R02,A | ;load the value in ACC to register R02 |

#### Example: use ACC for immediate addressing

| <u> </u> |          | 8                                                        |

|----------|----------|----------------------------------------------------------|

| LE       | DIA 30H  | ;load 30H to ACC                                         |

| AN       | NDIA 30H | ;perform 'AND' on ACC and 30H<br>;save the result to ACC |

| X        | ORIA 30H | ;perform 'XOR' on ACC and 30H<br>;save the result to ACC |

### Example: use ACC as the first operand of a dual operand instruction

| HSUBA | R01 | ;ACC-R01, save the result to ACC |

|-------|-----|----------------------------------|

| HSUBR | R01 | ;ACC-R01, save the result to R01 |

#### Example: use ACC as the second operand of a dual operand instruction

| SUBA | R01 | ;R01-ACC, save the result to ACC |

|------|-----|----------------------------------|

| SUBR | R01 | ;R01-ACC, save the result to R01 |

## 2.5 Program status register (STATUS)

STATUS register includes:

- ◆ ALU arithmetic status

- Reset status

Just like other registers, STATUS register can be the target register of any instruction. If an instruction that affects Z, DC or C bit that use STATUS as target register, then it cannot write on these 3 status bits. These bits are cleared or set to 1 according to device logic. TO and PD bit also cannot be written. Hence the instructions which use STATUS as target instruction may not result in what is predicted.

For example, CLRSTATUS will clear the high 3 bits and set the Z bit to 1. Hence the value of STATUS will be 000uu1uu (u will not change). It is recommended to only use CLRB, SETB, SWAPA and SWAPR instructions to change STATUS register because these will not affect any status bits.

#### Program status register STATUS (03H)

| •           | •    | `    | ,    |      |      |      |      |      |

|-------------|------|------|------|------|------|------|------|------|

| 03H         | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| STATUS      | IRP  | RP1  | RP0  | TO   | PD   | Z    | DC   | С    |

| R/W         | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset value | 0    | 0    | 0    | 1    | 1    | Χ    | Χ    | Χ    |

Bit7 IRP: Register memory select bit (indirect addressing)

1= Unused

0= Bank0 and Bank1 (00h~FFh)

Bit6~Bit5 RP[1:0]: Memory select bit

00= Select Bank0 01= Select Bank1 10= Unused

11= Unused

Bit4 TO: Time out bit;

1= Power on or CLRWDT instruction or STOP instruction

0= WDT time out

Bit3 PD: Power down bit

1= Power on or CLRWDT instruction

Execute STOP instruction

Bit2 Z: Result bit

1= The result of an arithmetic or logical operation is zero

0= The result of an arithmetic or logical operation is not zero

Bit1 DC: Half carry bit/borrow bit

1= Carry happens from the lower 4 bits to the higher bits, or no borrow from the lower 4 bits.

0= No carry from the lower 4 bits to the higher bits, or borrow from the lower 4 bits to the higher bits.

Bit0 C: Carry/borrow bit

1= A carry from the highest bit, or no borrow.

0= No carry from the highest bit, or a borrow hanppens.

The TO and PD flag bits can reflect the reason for chip reset. The following lists the events that affect the TO and PD and the status of the TO and PD after various resets.

| Event              | TO | PD |

|--------------------|----|----|

| Power on           | 1  | 1  |

| WDT overflow       | 0  | Χ  |

| STOP instruction   | 1  | 0  |

| CLRWDT instruction | 1  | 1  |

| Sleep              | 1  | 0  |

| TO | PD | Reset reason                    |

|----|----|---------------------------------|

| 0  | 0  | WDT overflow in sleep state     |

| 0  | 1  | WDT overflow in non-sleep state |

| 1  | 1  | Power on                        |

|    |    |                                 |

Status of TO/PD after reset

## 2.6 Pre-scaler (OPTION\_REG)

The OPTION\_REG register is a readable/writable register that contains various control bits for configuration.

- ♦ WDT pre-scaler

- External interrupt trigger edge

### Prescaler control register OPTION\_REG (01H)

| 01H         | Bit7     | Bit6   | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------------|----------|--------|------|------|------|------|------|------|

| OPTION_REG  | TOLSE_EN | INTEDG | T0CS | T0SE | PSA  | PS2  | PS1  | PS0  |

| R/W         | R/W      | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset value | 0        | 1      | 1    | 1    | 1    | 0    | 1    | 1    |

| Bit7      | T0LSE_EN: | TIMER0 clock source select F <sub>LSE</sub> enable bit                              |

|-----------|-----------|-------------------------------------------------------------------------------------|

|           | 0=        | TIMER0 clock source is determined by T0CS                                           |

|           | 1=        | TIMER0 clock source select FLSE                                                     |

| Bit6      | INTEDG:   | Trigger interrupt edge selection bit                                                |

|           | 0=        | INT pin falling edge trigger interrupt                                              |

|           | 1=        | INT pin rising edge trigger interrupt                                               |

| Bit5      | T0CS:     | TIMER0 clock source select bit                                                      |

|           | 0=        | Internal instruction period clock (F <sub>CPU</sub> )                               |

|           | 1=        | Transition edge on the T0CKI pin                                                    |

| Bit4      | T0SE:     | TIMER0 clock source edge select bit                                                 |

|           | 0=        | Incremented when the signal at the T0CKI pin jumps from a low level to a high level |

|           | 1=        | Incremented when the signal at the T0CKI pin jumps from a high level to a low level |

| Bit3      | PSA:      | Pre-scaler allocation bit                                                           |

|           | 0=        | Allocate pre-scaler to TIMER0 module                                                |

|           | 1=        | Allocate pre-scaler to WDT                                                          |

| Bit2~Bit0 | PS2~PS0:  | Pre-allocation parameter configure bit                                              |

|           |           |                                                                                     |

| PS2 | PS1 | PS0 | TMR0 frequency division ratio | WDT frequency division ratio |

|-----|-----|-----|-------------------------------|------------------------------|

| 0   | 0   | 0   | 1:2                           | 1:1                          |

| 0   | 0   | 1   | 1:4                           | 1:2                          |

| 0   | 1   | 0   | 1:8                           | 1:4                          |

| 0   | 1   | 1   | 1:16                          | 1:8                          |

| 1   | 0   | 0   | 1:32                          | 1:16                         |

| 1   | 0   | 1   | 1:64                          | 1:32                         |

| 1   | 1   | 0   | 1:128                         | 1:64                         |

| 1   | 1   | 1   | 1:256                         | 1:128                        |

|     |     |     |                               |                              |

The pre-scaler register is an 8-bit counter. When surveil on register WDT, it is a postscaler; when it is used as a timer or counter, it is called pre-scaler. There is only 1 physical scaler and can only be used for WDT or TIMER0, but not at the same time. This means that if it is used for TIMER0, the WDT cannot use pre-scaler and vice versa.

When used for WDT, the CLRWDT instruction will clear pre-scaler and WDT timer.

When used for TIMER0, all instructions related to writing to TIMER0 (such as: CLR TMR0, SETB TMR0,1) will clear the pre-scaler.

## 2.7 Program counter (PC)

The program counter (PC) controls the instruction sequence in program memory FLASH, it can address in the whole range of FLASH. After obtaining the instruction code, the PC will increase by 1 and point to the address of the next instruction code. When executing jump, condition jump, loading value to PCL, subroutine call, initializing reset, interrupt, interrupt return, subroutine return and other actions, the PC will load the address which is related to the instruction, rather than the address of the next instruction.

When encountering a condition jump instruction and the condition is met, the next instruction to be read during current instruction execution will be discarded and an empty instruction period will be inserted. After this, the correct instruction can be obtained. If not, the next instruction is executed in sequence.

The program counter (PC) is 11-bit width, users can access lower 8 bits by PCL (02H). The higher 3 bits cannot be accessed. It can hold address for  $2K \times 16Bit$  program. Loading a value to PCL results in a short jump to the 256 addresses of the current page.

Note: When the programmer uses PCL to make a short jump, the programmer must first load a value to the PC high bit buffer register PCLATH.

The PC values for several special cases are given below

| Reset              | PC=0000;                                                                         |  |  |  |

|--------------------|----------------------------------------------------------------------------------|--|--|--|

| Interrupt          | PC=0004 (original PC+1 will be add to stack automatically);                      |  |  |  |

| CALL               | PC=Program specified address (original PC+1 will be add to stack automatically); |  |  |  |

| RET, RETI, RETI    | PC=Value from stack;                                                             |  |  |  |

| PCL operation      | PC[10:8] unchanged, PC[7:0]=user defined value;                                  |  |  |  |

| JP                 | PC=Program specified value;                                                      |  |  |  |

| Other instructions | PC=PC+1;                                                                         |  |  |  |

## 2.8 Watchdog timer (WDT)

The Watch Dog Timer (WDT) is an on-chip self-oscillating RC oscillator timer, without any peripheral components. Even if the chip's main clock stops working, the WDT can also keep time. The WDT overflow will generate a reset.

### 2.8.1 WDT period

The WDT uses an 8-bit prescaler. After all resets, the WDT overflow period is 128ms, and the WDT overflow period is calculated as 16ms\*dividing factor. Setting the OPTION\_REG register will change the WDT period, and the WDT overflow period will be affected by the ambient temperature, power supply voltage and other parameters.

The "CLRWDT" and "STOP" instructions clear the WDT timer and the count value in the prescaler (when the prescaler is assigned to the WDT). WDT generally is used to prevent the system and MCU program from being out of control. Under normal circumstances, the WDT should be cleared by the "CLRWDT" instruction before it overflows to prevent a reset. If program is out of control for some reason such that "CLRWDT" instruction is not able to execute before overflow, WDT overflow will then generate a reset to make sure the system restarts. If a reset is generated by the WDT overflow, then 'TO' bit of STATUS will be cleared to 0. Users can judge whether the reset is caused by WDT overflow according to this.

#### Note:

- If WDT is used, 'CLRWDT' instruction must be placed somewhere is the program to make sure

it is cleared before WDT overflow. If not, chip will keep resetting and the system cannot be

operated normally.

- 2. It is not allowed to clear WDT during interrupt so that the main program 'run away' can be detected.

- The program should have one WDT clearing operation in the main program, and try not to clear the WDT in multiple branches, this architecture can maximize the protection function of the watchdog counter.

- 4. The overflow time of the watchdog counter varies from chip to chip, so when setting the clear WDT time, there should be a greater redundancy with the WDT overflow time to avoid an unnecessary WDT reset.

### 2.8.2 Registers related to watchdog control

Oscillation control register OSCCON (14H)

| 14H         | Bit7 | Bit6  | Bit5  | Bit4  | Bit3 | Bit2 | Bit1   | Bit0 |

|-------------|------|-------|-------|-------|------|------|--------|------|

| OSCCON      |      | IRCF2 | IRCF1 | IRCF0 |      |      | SWDTEN |      |

| R/W         |      | R/W   | R/W   | R/W   |      |      | R/W    |      |

| Reset value |      | 1     | 0     | 1     |      |      | 1      |      |

Bit7 Unused.

Bit6~Bit4 IRCF<2:0>: Internal oscillator frequency selection bit

111= Fsys = Fhsi/1110= Fsys = Fhsi/2

101= F<sub>SYS</sub> = F<sub>HSI</sub>/4 (default)

$\begin{array}{lll} 100 = & F_{SYS} = F_{HSI}/8 \\ 011 = & F_{SYS} = F_{HSI}/16 \\ 010 = & F_{SYS} = F_{HSI}/32 \\ 001 = & F_{SYS} = F_{HSI}/64 \\ 000 = & F_{SYS} = 32KHz(F_{LSI}) \end{array}$

Bit3~Bit2 Unused

Bit1 SWDTEN: Software enable or disable watchdog timer bit

1= Enable WDT0= Disable WDT

Bit0 Unused

Note: If the WDT configuration bit in CONFIG = 1, WDT is always enabled, regardless of the state of the SWDTEN control bit. If the WDT configuration bit in CONFIG = 0, the SWDTEN control bit can be used to enable or disable WDT.

# 3. System Clock

### 3.1 Overview

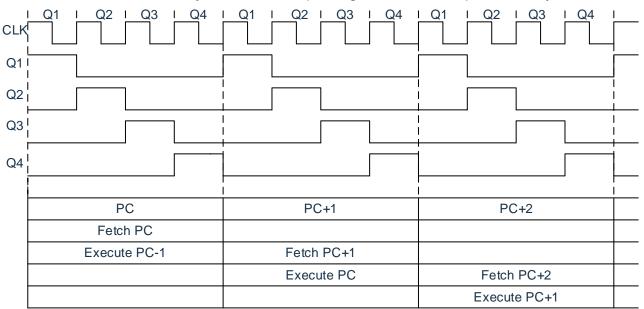

The clock signals are generated by an oscillator, which generates 4 non-overlapping quadrature clock signals, called Q1, Q2, Q3, and Q4. Each Q1 inside the IC increments the program counter (PC) by one, and Q4 removes the instruction from the program memory cell and locks it into the instruction register. The removed instruction is decoded and executed between the next Q1 and Q4, which means that it takes 4 clock cycles to execute an instruction. The following figure represents the clock versus instruction cycle execution timing diagram.

An instruction cycle contains four Q-cycles, and the instruction execution and fetching are in pipeline structure, fetching finger occupies one instruction cycle, while decoding and execution occupy another instruction cycle, but due to the pipeline structure, from a macro point of view, the effective execution time of each instruction is one instruction cycle. If an instruction causes the program counter address to change (e.g. JP) then the prefetched instruction opcode is invalid and it takes two instruction cycles to complete the instruction, which is the reason why all instructions operating on the PC take up two clock cycles.

Figure 3-1: Clock and instruction cycle timing chart (F<sub>CPU</sub> DIV=4T)

Following is the relationship between working frequency of system and the speed of instructions when  $F_{CPU}$  DIV=4T:

| System frequency (Fsys) | Dual instruction period | Single instruction period |

|-------------------------|-------------------------|---------------------------|

| 1MHz                    | 8µs                     | 4µs                       |

| 2MHz                    | 4µs                     | 2µs                       |

| 4MHz                    | 2µs                     | 1µs                       |

| 8MHz                    | 1µs                     | 500ns                     |

| 16MHz                   | 500ns                   | 250ns                     |

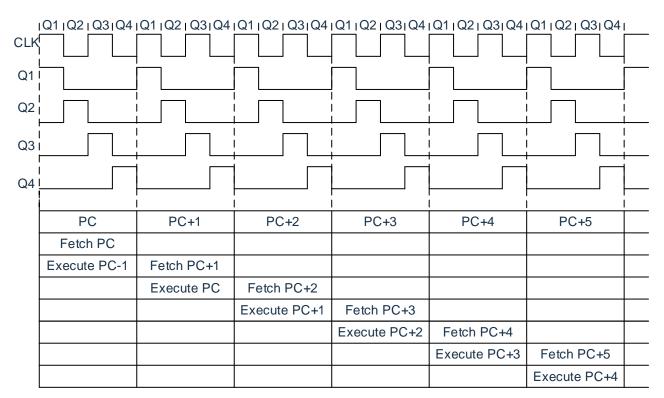

Figure 3-2: Clock and instruction cycle timing chart (F<sub>CPU</sub>\_DIV=2T)

Following is the relationship between working frequency of system and the speed of instructions when  $F_{CPU}$ DIV=2T:

| System frequency (Fsys) | Dual instruction period | Single instruction period |

|-------------------------|-------------------------|---------------------------|

| 1MHz                    | 4µs                     | 2µs                       |

| 2MHz                    | 2µs                     | 1µs                       |

| 4MHz                    | 1µs                     | 500ns                     |

| 8MHz                    | 500ns                   | 250ns                     |

| 16MHz                   | 250ns                   | 125ns                     |

# 3.2 System oscillator

The chip has one type of oscillation: internal RC oscillation.

### 3.2.1 Internal RC oscillation

The default oscillation mode of the chip is internal RC oscillation, and the oscillation frequency is fixed at 16MHz. On this basis, the operating frequency of the chip can be set through the OSCCON register.

### 3.3 Reset time

The reset time is the time from the chip reset to the chip oscillation stabilization, its design value is about 16ms.

Note: Reset time exists for both power on reset and other resets.

## 3.4 Oscillator control register

The Oscillator Control (OSCCON) register controls the system clock and frequency selection.

Oscillator control register OSCCON (14H)

| 14H         | Bit7 | Bit6  | Bit5  | Bit4  | Bit3 | Bit2 | Bit1   | Bit0 |

|-------------|------|-------|-------|-------|------|------|--------|------|

| OSCCON      | -    | IRCF2 | IRCF1 | IRCF0 |      |      | SWDTEN |      |

| R/W         |      | R/W   | R/W   | R/W   |      |      | R/W    |      |

| Reset value |      | 1     | 0     | 1     |      |      | 1      |      |

| Bit7      | Unused     |                                               |

|-----------|------------|-----------------------------------------------|

| Bit6~Bit4 | IRCF<2:0>: | Internal oscillator frequency selection bit   |

|           | 111=       | Fsys = F <sub>HSI</sub> /1                    |

|           | 110=       | Fsys = F <sub>HSI</sub> /2                    |

|           | 101=       | Fsys = F <sub>HSI</sub> /4 (default)          |

|           | 100=       | Fsys = Fhsi/8                                 |

|           | 011=       | Fsys = Fhsi/16                                |

|           | 010=       | $F_{SYS} = F_{HSI}/32$                        |

|           | 001=       | Fsys = Fhsi/64                                |

|           | 000=       | F <sub>SYS</sub> = 32KHz (LFINTOSC)           |

| Bit3~Bit2 | Unused.    |                                               |

| Bit1      | SWDTEN:    | Software enable or disable watchdog timer bit |

|           | 1=         | Enable WDT                                    |

|           | 0=         | Disable WDT                                   |

| Bit0      | Unused     |                                               |

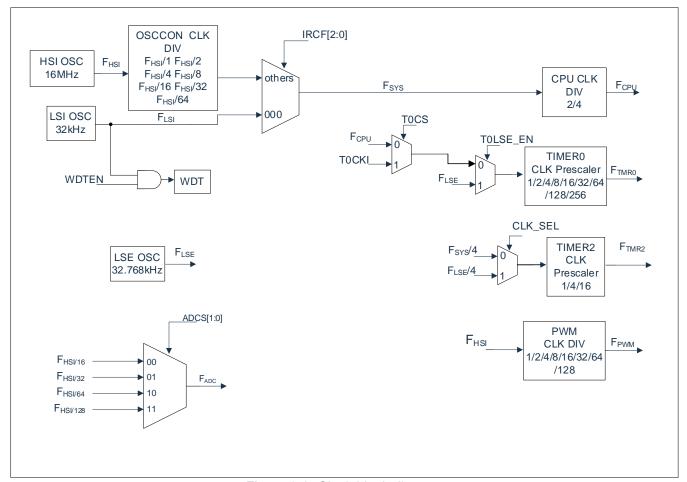

## 3.5 Clock block diagram

Figure 3-3: Clock block diagram

## 4. Reset

The chip can be reset in the following 4 ways:

- Power on reset

- External reset

- LVR reset

- Watchdog overflow reset during normal operation

When any of the above reset occurs, all system registers will be restored to their default state, the program will stop running, and the program counter (PC) will be cleared to zero. At the same time, the program will start running from reset vector 0000H after the reset. The TO and PD flags of STATUS can give information about the reset state of the system (see the description of STATUS for details), and the user can control the program execution path according to the state of PD and TO.

Any kind of reset situation requires a certain response time, and the system provides a completed reset process to ensure that the reset action is carried out smoothly.

#### 4.1 Power on reset